# **Novoptel**

# Application note 6 Firmware Update using XILINX Impact

**Revision history**

| Version | Date       | Remarks                   | Author  |

|---------|------------|---------------------------|---------|

| 0.9.0   | 02.08.2016 | Draft version             | B. Koch |

| 0.9.1   | 26.06.2021 | Digilent programmer added | R. Noe  |

| 0.9.2   | 06.07.2021 | SPI flash memory added    | R. Noe  |

| 0.9.3   | 05.06.2024 | Xilinx Vivado added       | B. Koch |

|         |            |                           |         |

#### **Contents**

#### Summary

- 1. Connect the XILINX programmer to the PC

- 2. Verify the XILINX cable driver

- 3. Connect the XILINX programmer to the Novoptel device

- 4. Open XILINX Impact

- 5. Program device

- 5.1 JTAG chain with FPGA and flash memory

- 5.2 JTAG with FPGA and attached SPI flash memory

- 6. Usage of Digilent HTAG-HS2 rev. A programmer

- 7. Firmware Update with XILINX Vivado

## **Summary**

This document describes the firmware update of Novoptel instruments using XILINX Platform Cable USB II, or Digilent HTAG-HS2 rev. A, and XILINX Impact.

Novoptel GmbH EIM-E Warburger Str. 100 33098 Paderborn Germany www.novoptel.com

Novoptel reserves the right to change the content.

# 1. Connect the XILINX programmer to the PC

Fig. 1: XILINX Platform Cable USB II

Use a USB cable to connect the programmer box to the PC. Windows should automatically detect the hardware and install the driver.

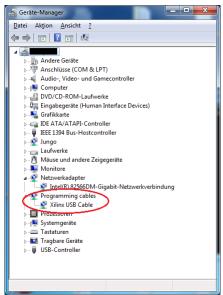

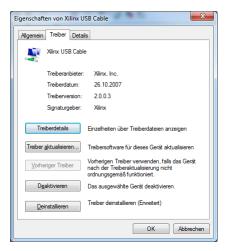

## 2. Verify the XILINX cable driver

If the driver is installed correctly, the LED on the programmer box will glow in orange color. The programmer device should appear in the Windows device manager.

Fig. 2: Windows device manager

The driver version can be verified in the device properties.

# 3. Connect the XILINX programmer to the Novoptel device

Use the flat ribbon cable to connect the XILINX programmer to the JTAG socket at the rear side of the Novoptel device. Power the Novoptel device. If the connection is correct, the LED on the programmer box will glow in color green as soon as the Novoptel device is powered.

## 4. Open XILINX Impact

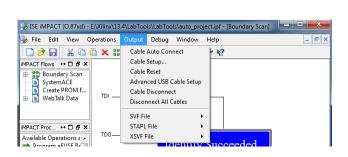

If the programmer box is connected to a powered Novoptel device, XILINX Impact should be able to automatically detect the programmer.

Fig. 3: Cable setup in XILINX Impact

Create a new project in XILINX Impact. If the programmer is not detected by XILINX Impact, check the configuration setup by opening the "Cable Setup..." in the menu bar. If the programmer is detected, Impact should automatically initialize the JTAG chain. If not, select "File"->"Initialize Chain" in the menu bar.

If the programmer box is connected to a powered Novoptel device, XILINX Impact should be able to automatically detect the programmer.

#### 5. Program device

#### 5.1 JTAG chain with FPGA and flash memory

Most Novoptel devices until about 2017 contained a JTAG chain with FPGA and flash memory. This is discussed here.

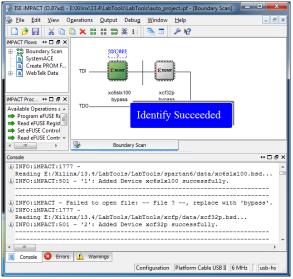

Fig. 4: Correct JTAG chain in XILINX Impact

If the JTAG chain is initialized correctly, two devices should be accessible. An FPGA (e.g. xc6sxl100) and a flash memory (e.g. xcf32p). The FPGA can be programmed using a .bit file to test new firmwares

without overwriting the old one until you cycle the power. The flash memory can be programmed with a .mcs file to permanently upgrade the firmware. The .bit and .mcs files are provided by Novoptel upon request. Right-click on a device and select "Assign New Configuration File..." to assign a file.

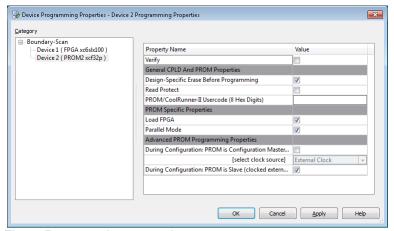

Fig. 5: Programming properties

Before programming the .mcs file, verify the programming properties. Right-click on the flash memory and select "Set Programming Properties...". It is important that the menu item "Design-Specific Erase Before Programming" is activated, see Fig. 5. Finally the programming is started by right-clicking the device and selecting "Program".

# 5.2 JTAG with FPGA and attached SPI flash memory

Most Novoptel devices since about 2018 contain a JTAG chain with only an FPGA that has attached flash memory. This is discussed here. Example is a PM1000 built in 2021 and to be updated to firmware "polarimeter88\_v1070\_r137".

Before you can program such a device, one environment variable must be set. In Windows 10:

- Click Windows Logo or Search and type "env".

- Select "Edit the system environment variables".

- The window "System Properties" appears.

- At the bottom click "Environment Variables ...".

- Press "New ..." and define/edit the variable "XIL IMPACT SKIPIDCODECHECK" with the value "1".

Fig. 6: Editing environment variable

- Press "OK" to close each window.

#### Then:

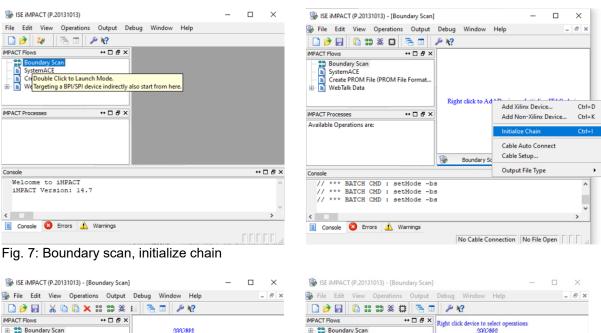

- Launch XILINX Impact.

- Select "Boundary scan".

- Double-click "Boundary scan".

- Right-click to "Initialize chain". After "Identify Succeeded", in this example XC6SLX150, you may close the pop-up window "Device Programming Properties".

- Right-click the FPGA (is or gets green) to "Assign New Configuration File ...".

- Assign the firmware bitfile, here "polarimeter88\_v1070\_r137.bit". We propose you first test this bitfile. So, for the time being, you say "No" to "Assign SPI or BPI PROM".

Boundary Scan

SystemACE

Create PROM File (PROM File Format... Boundary Scan

SystemACE

Create PROM Fi SystemACE

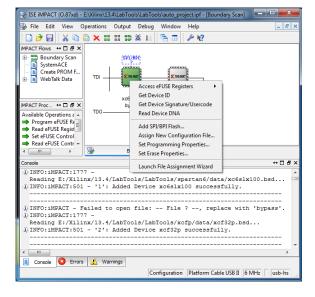

Create PROM File (PROM File Format. Access eFUSE Registers Get Device ID Get Device Signature/Usercode Read Device DNA iMPACT Processes ↔□♂× iMPACT Processes ↔□♂× TDO. Available Operations are:

Program eFUSE Registe Attach SPI or BPI PROM

Read eFUSE Registers

Set eFUSE Control Regi

Read eFUSE Control Regi

Get Device Signature/U Add SPI/BPI Flash Available Operations are: Program eFUSE Registers...

Read eFUSE Control Register...

Read eFUSE Control Register...

Read eFUSE Control Register...

Read eFUSE Control Register... Set Programming Properties Set Erase Properties Launch File Assignment Wizard PROGRESS\_END - End Operation.

Elapsed time = 0 sec.

// \*\*\* BATCH CMD : identifyMPM DINFO: iMPACT: 501 - '1': Added Device xc6slx150 successfully. Console Errors 🗘 Warnings Console Errors Marnings Configuration Platform Cable USB II 6 MHz usb-hs Configuration Platform Cable USB II 6 MHz usb-hs

Fig. 8: Assign configuration file

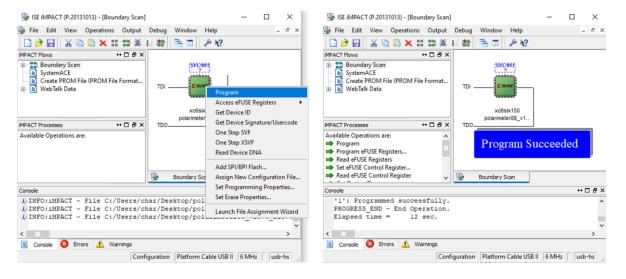

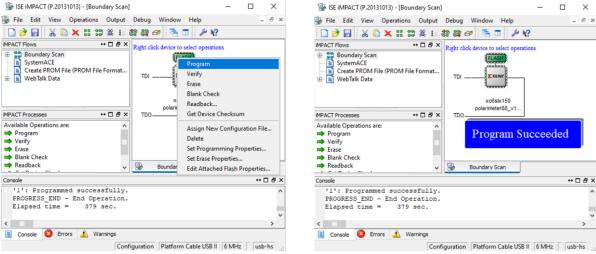

- Right-click the FPGA (gets green) to "Program". "Cancel" the pop-up window "Device Programming Properties". After a while (here: 12 s) you see "Program Succeeded". You can test now the firmware on the FPGA. But if you switch off the device and power on again, the old .mcs file will automatically be loaded as firmware from the SPI flash memory into the FPGA.

Fig. 9: Program FPGA

If the firmware works satisfactorily you should program it permanently into the SPI flash memory (which takes much longer):

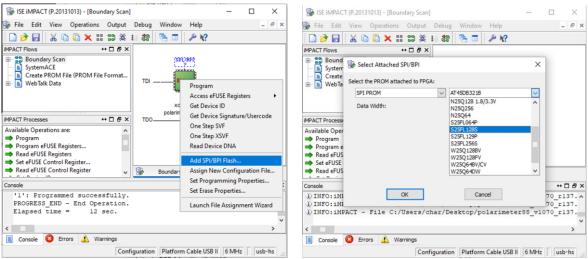

- Right-click the FPGA to "Assign SPI/BPI flash...", here "polarimeter88\_v1070\_r137.mcs".

- To "Select Attached SPI/BPI", select Data Width "4" for an "SPI PROM", here "S25FL128S". Click OK.

Fig. 10: Assign SPI flash memory file and device

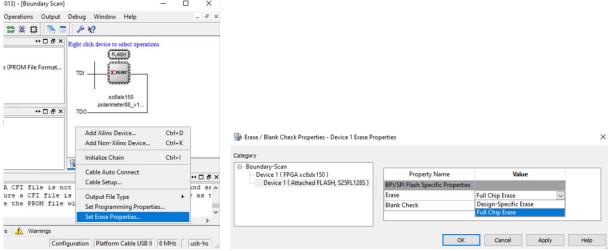

- The attached flash memory is now shown. Right-click to "Set Erase Properties...". In the next window, click "Device 1 (Attached FLASH S25FL128S)" and set the property "Erase" to the value "Full Chip Erase" (not "Device-Specific Erase"). Then click "OK".

Fig. 11: Set erase properties

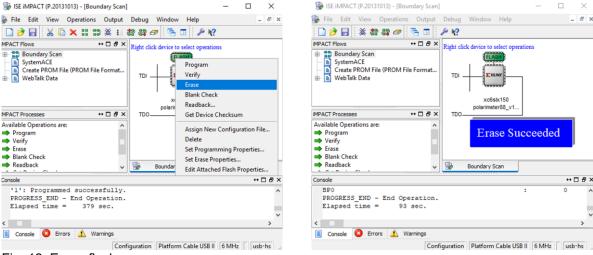

- The flash memory is now shown. Right-click the "FLASH" to "Erase". After some time (here: 93 s) you see "Erase Succeeded".

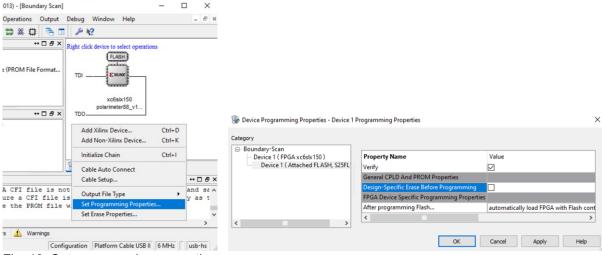

- Right-click to "Set Programming Properties...". In the next window, click "Device 1 (Attached FLASH S25FL128S)" and uncheck the (initially checked) property "Design-Specific Erase Before Programming". Then click "OK".

- Right-click the flash memory "FLASH" to "Program" it. After some time (here: 379 s) you see "Programming Succeeded". You may close all windows. Upon power-up this .mcs file will be loaded into the FPGA.

Fig. 12: Erase flash memory

Fig. 13: Set programming properties

Fig. 14: Program flash memory

# 6. Usage of Digilent HTAG-HS2 rev. A programmer

The Digilent HTAG-HS2 rev. A Programming Cable for Xilinx® FPGAs (instead of XILINX Platform Cable USB II) can also be used together with XILINX Impact.

Digilent provides a plugin for their programmers with the Xilinx software:

https://reference.digilentinc.com/lib/exe/fetch.php?tok=0cf116&media=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2F%2Ffiles.digilent.com/sepsidesedia=http%3A%2Ffiles.digilent.com/sepsidesedia=http%3A%2Ffiles.digilent.com/sepsidesedia=http%3A%2Ffiles.digilent.com/sepsidesedia=http%3A%2Ffiles.digilent.com/sepsidesedia=http%3A%2Ffiles.digilent.com/sepsidesedia=http%3A%2Ffiles.digilent.com/sepsidesedia=http%3A%2Ffiles.digilent.com/sepsidesedia=http%3A%2Ffiles.digilent.com/sepsidesedia=http%3A%2Ffiles.digilent.com/sepsidesedia=http%3A%2Ffiles.digilent.com/sepsidesedia=http%3A%2Ffiles.digilent.com/sepsidesedia=http%3A%2Ffiles.digilent.com/s

https://reference.digilentinc.com/reference/software/digilent-plugin-xilinx-tools/start

Quoting from a Digilent manual:

The Digilent Plug-in can be installed in the ISE installation directory by copying libCseDigilent.dll (libCseDigilent.so on Linux systems) and libCseDigilent.xml to the plugins directory. For the Windows version of ISE Design Suite, the typical location is

C:\Xilinx\14.1\ISE\_DS\ISE\lib\nt\plugins\Digilent\libCseDigilent. For 64-bit Windows, use nt64 in place of nt.

After this procedure, XILINX Impact should be able to recognize FPGA and memory through the Digilent programmer.

#### 7. Firmware Update with XILINX Vivado

Later Novoptel instruments may contain a XILINX Series 7 FPGA such as Artix. In this case XILINX Vivado is required instead of Impact for permanently programming the .mcs file to the flash memory. Please note that XILINX Impact still can temporarily program the .bit file to some of the Artix FPGAs.

Download the latest "Vivado Lab Solutions" from https://www.xilinx.com/support/download.html.

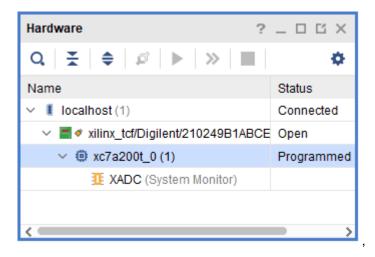

Open "Hardware Manager" in XILINX Vivado. Click on "Open Target" -> "Auto Connect". The software should connect to the FPGA and show it in the "Hardware" section:

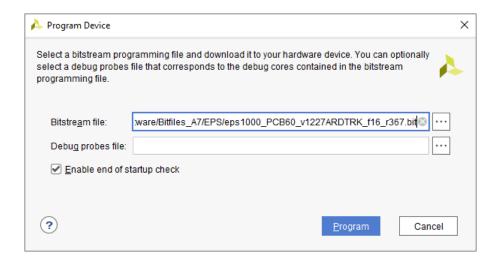

To temporarily load a .bit file to the FPGA, right-click the FPGA (xc7a200t) and select "Program Device...":

Select the desired .bit file and click "Program". Done!

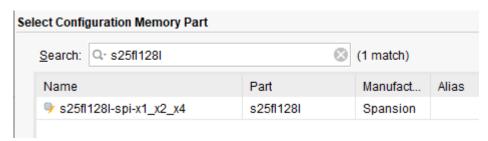

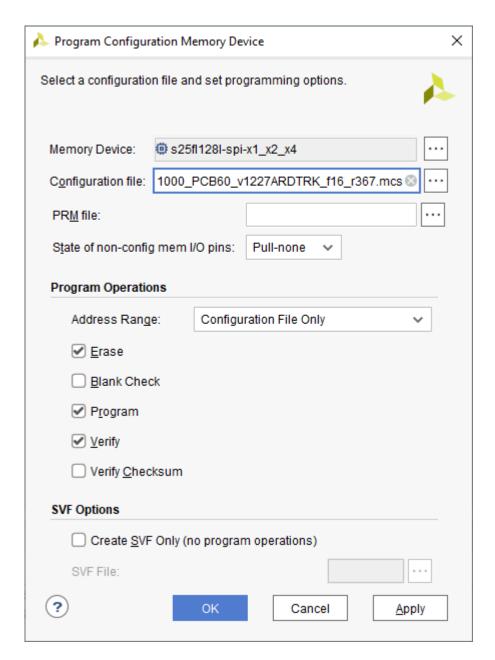

To permanently store the .mcs file in the flash memory, right-click on the FPGA again and select "Add Configuration Memory Device…". Select "mx25l12872f-spi-x1\_x2\_x4" (LU1000 devices only) or "s25fl128l" (all other devices):

Select the desired .mcs-file and click "OK":

After the flash programming process finished, the FPGA is not programmed yet! To load the program the FPGA you can either unplug the JTAG cable from the instrument and toggle the instrument's power, or right-click on the FPGA in the Vivado software and select "Boot from Configuration Memory Device".